A J-K flop-flop has two data/control inputs, and a. It is usually constructed out of pair of S-R latches, one after the other, along with some additional gates. It samples the input on either the rising or falling edge of the clock depending on the variety). The truth table for a positive-edge triggered D flip-flop shows an up arrow to remind you that it is sensitive to its D input only on the rising edge of the clock otherwise it is latched. A D flop-flop has a single data input, and a clock input.

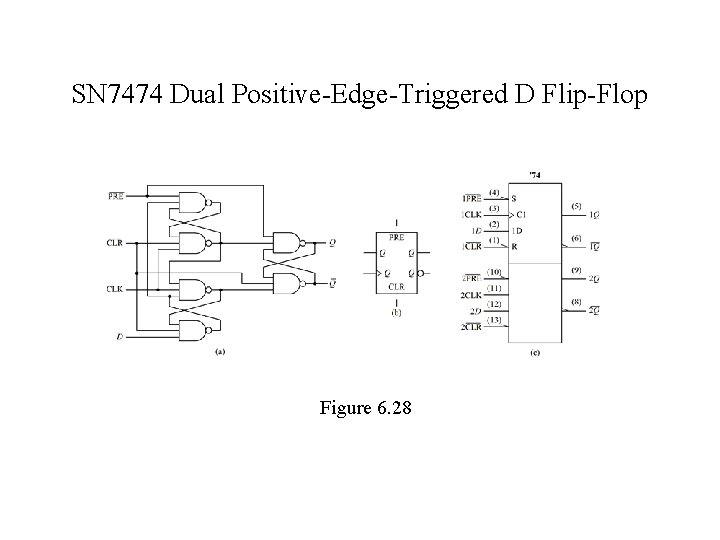

This chip has inputs to asynchronously clear and set the flip-flop's data. The schematic symbol for a 7474 edge-triggered D flip-flop is shown below. In the timing diagram it can be seen that the value on D is the same as. The outputs Q and Qn are the flip-flop's stored data and the complement of the flip-flop's stored data respectively. The triggering occurs at a voltage level and is not directly related to the transition time of the rising edge of the clock. The information on the D input is accepted by the flip-flops on the positive going edge of the clock pulse. The inverse of the stored value is fed back into the device input, so that on each rising edge of Clk the stored value changes. This device contains two independent positive-edge-triggered D-type flip-flops with complementary outputs. I need a flip-flop like this, since I need Preset and Clear asynchronous inputs. The exact flip-flop design that Im using is the SN7476 from TI. The Integrated-Circuit D Flip-Flop (7474) A simple circuit with 1 edge-triggered flip-flop is shown in the figure with an example timing diagram to the right. Hi guys, Im simulating a circuit which uses a few (actually, 10) Positive-Edge-Triggered JK flip flops. When Q follows D (latch enabled) the latch is said to be transparent. 7474 dual D-type positive edge-triggered flip-flop with clear and preset.The 7475 contains 4 transparent D latches with a common enable (gate) on latches 0 and 1 and another common enable on latches 2 and 3.

0 kommentar(er)

0 kommentar(er)